Morpher Tutorial

Code Repo: https://github.com/ecolab-nus/morpher

Organizers

Zhaoying Li, Dhananjaya Wijerathne, Tulika Mitra

from National University of Singapore

Introduction

Coarse-Grained Reconfigurable Architecture (CGRA) provides a promising pathway to scale the performance and energy efficiency of computing systems by accelerating the compute-intensive loop kernels. However, there exists no end-to-end open-source toolchain for CGRA, supporting architectural design space exploration, compilation, simulation, and FPGA emulation for real-world applications.

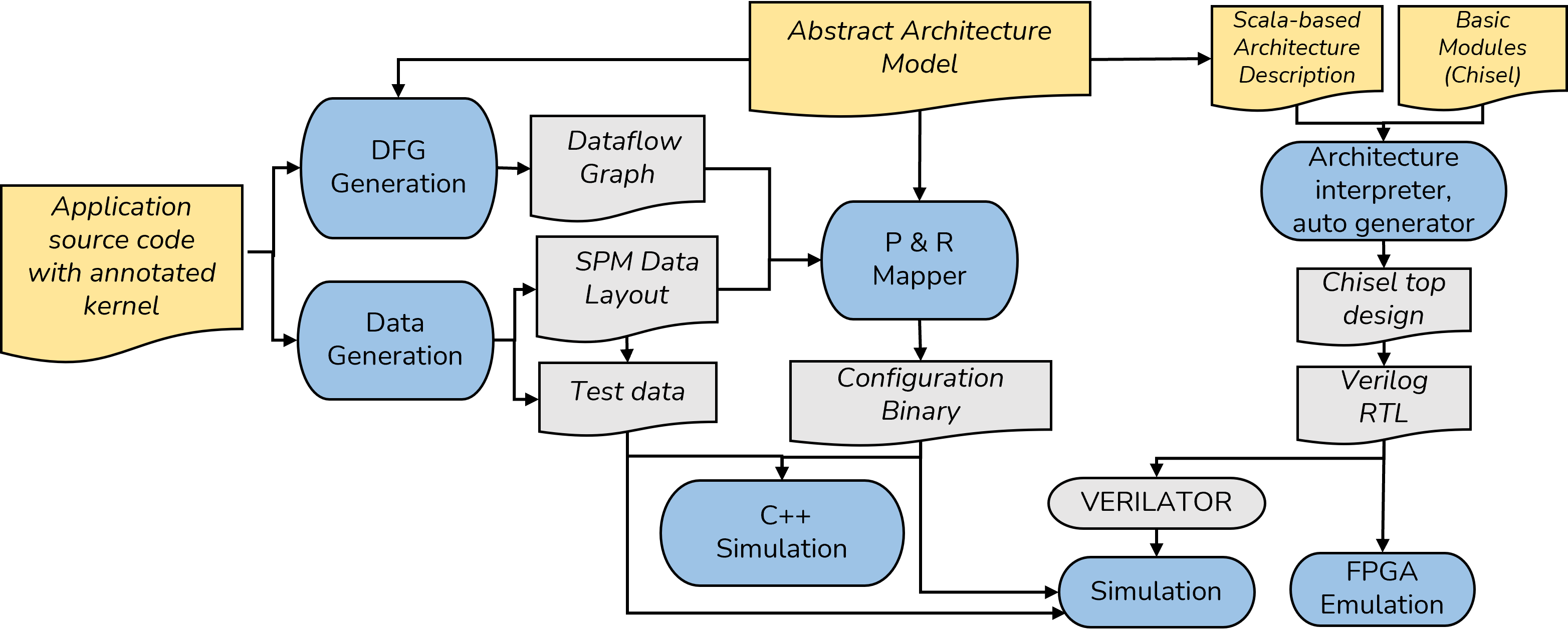

This hands-on tutorial presents Morpher, an open-source end-to-end compilation and simulation framework for CGRA, featuring state-of-the-art mappers, assisting in design space exploration, and enabling application-level testing of CGRA.

Morpher can take a real-world application with a compute-intensive kernel and a user-provided CGRA architecture as input, compile the kernel using different mapping methods, and automatically validate the compiled binaries through cycle-accurate simulation using test data extracted from the application.

Morpher can handle real-world application kernels without being limited to simple toy kernels through its feature-rich compiler.

Morpher architecture description language allows users to easily specify a variety of architectural features such as complex interconnects, multi-hop routing, and memory organizations.

Fig.1 Morpher Framework

Goal

- Learn the current status of CGRA

- Learn the Morpher framework

- Hands-on tutorial for Morpher

Requirement

- Hardware: Linux machine or Mac (Intel chip)

- Software: Docker

Schedule

- Introduction (30min)

a. The era of domain-specific ASIC Accelerators.

b. Software-defined hardware.

c. Morpher: an end-to-end CGRA toolchain. - CGRA Architecture (40min)

a. The diversity of CGRA architecture, including network, configurability, memory access, and heterogeneity.

b. Modular CGRA Architecture: Processing Elements, Function Unit, and Datapath.

c. An example to write your own CGRA specification: neighbor-to-neighbor network, and one-cycle multiple-hops network. - Application and Compilation Flow (30min)

a. Data-flow Graph Generation: how to annotate the target loop, and generate the corresponding operations for each instruction.

b. Hands-on Exercise: An example for microspeech application. - CGRA Mapper (30min)

a. Modulo Routing Resource Graph: time-extended resource graph of the hardware, and modulo scheduling.

b. Mapping of a DFG. We introduce three mappers: PathFinder, Simulated Annealing, and LISA (from HPCA 2022). - Simulator, FPGA Emulator, and SOC design (30min)

a. Binary Generation: the configuration bits for hardware

b. Cycle-accurate C++ simulator: data trace generation.

c. Data Transfer and FPGA Emulation: SPI data transfer and SOC emulation with FPGA.

Related publications

[WOSET] Morpher: An Open-Source Integrated Compilation and Simulation Framework for CGRA

Dhananjaya Wijerathne, Zhaoying Li, Manupa Karunaratne, Li-Shiuan Peh, Tulika Mitra

Workshop on Open-Source EDA Technology 2022

[DAC] PANORAMA: Divide-and-Conquer Approach for Mapping Complex Loop Kernels on CGRA

Dhananjaya Wijerathne, Zhaoying Li, Thilini Kaushalya Bandara, Tulika Mitra

59th ACM/IEEE Design Automation Conference, 2022 Publicity Paper

Artifact Link

[HPCA] LISA: Graph Neural Network based Portable Mapping on Spatial Accelerators

Zhaoying Li, Dan Wu, Dhananjaya Wijerathne, Tulika Mitra

28th IEEE International Symposium on High-Performance Computer Architecture, 2022

Artifact Link Distinguished Artifact Award

[ASPLOS] REVAMP: A Systematic Framework for Heterogeneous CGRA Realization

Thilini Kaushalya Bandara, Dhananjaya Wijerathne, Tulika Mitra, Li-Shiuan Peh

27th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, 2022

Artifact Link

[TCAD] HiMap: Fast and Scalable High-Quality Mapping on CGRA via Hierarchical Abstraction

Dhananjaya Wijerathne, Zhaoying Li, Anuj Pathania, Tulika Mitra, Lothar Thiele

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 41(10) 2022

[TCAD] ChordMap: Automated Mapping of Streaming Applications onto CGRA

Zhaoying Li, Dhananjaya Wijerathne, Xianzhang Chen, Anuj Pathania, Tulika Mitra

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 41(2) 2022

[Book Chapter] Coarse-Grained Reconfigurable Array (CGRA)

Zhaoying Li, Dhananjaya Wijerathne, Tulika Mitra

Book chapter in “Handbook of Computer Architecture”, Springer (Invited)

[DATE] HiMap: Fast and Scalable High-Quality Mapping on CGRA via Hierarchical Abstraction

Dhananjaya Wijerathne, Zhaoying Li, Anuj Pathania, Tulika Mitra, Lothar Thiele

Design Automation and Test in Europe 2021

[TECS] CASCADE: High Throughput Data Streaming via Decoupled Access/Execute CGRA

Dhananjaya Wijerathne, Zhaoying Li, Manupa Karunaratne, Anuj Pathania, Tulika Mitra

ACM Transactions on Embedded Computing Systems

Special Issue on ACM/IEEE International Conference on Compilers, Architecture, and Synthesis for Embedded Systems 2019

[ICCAD] 4D-CGRA : Introducing the branch dimension to spatio-temporal application mapping of CGRAs

Manupa Karunaratne, Dhananjaya Wijerathne, Tulika Mitra, Li-Shiuan Peh

38th ACM/IEEE International Conference on Computer Aided Design, November 2019

[A-SSCC] HyCUBE: a 0.9V 26.4 MOPS/mW, 290 pJ/cycle, Power Efficient Accelerator for IoT Applications

Bo Wang, Manupa Karunarathne, Aditi Kulkarni, Tulika Mitra, Li-Shiuan Peh

IEEE Asian Solid-State Circuits Conference, November 2019

[DAC] DNestMap : Mapping Deeply-Nested Loops on Ultra-Low Power CGRAs

Manupa Karunaratne, Cheng Tan, Aditi Kulkarni, Tulika Mitra, Li-Shiuan Peh

55th ACM/IEEE Design Automation Conference, June 2018

[DAC] HyCUBE : A CGRA with Reconfigurable Single-cycle Multi-hop Interconnect

Manupa Karunaratne, Aditi Kulkarni, Tulika Mitra, Li-Shiuan Peh

54th ACM/IEEE Design Automation Conference, June 2017

[ACM-TRETS] Graph Minor Approach for Application Mapping on CGRAs

Liang Chen, Tulika Mitra

ACM Transactions on Reconfigurable Technology and Systems 2014

[FPT] Graph Minor Approach for Application Mapping on CGRAs Much expanded journal version

Liang Chen, Tulika Mitra

International Conference on Field Programmable Technology, December 2012

Best Paper Award